什么是信号完整性?

当今使用的许多PCB布局和布线指南,即使是针对中等速度的信号和设备,也是为了确保信号完整性。如果您是PCB设计的新手,而且您从未遇到过信号完整性问题,那么在设计中确保信号完整性的概念可能显得很深奥。现代PCB可能会遇到许多问题,这些问题可以通过一些简单的布局实践来解决或预防。信号完整性实践的重点是识别和修复PCB布局布线中的这些问题,从而使数字或模拟信号在传播过程中不会失真,并且能够在互连的过程中得到恢复。

在本指南中,我们将简要概述PCB布局布线中可能出现的一些信号完整性问题,以及一些有助于解决这些问题的基本解决方案。在设计阶段的早期实施部分基本实践,要确保电路板布线后的信号完整性就会容易得多。

信号完整性基础知识

从最简单的意义上讲,将信号完整性实践实施到PCB布局和布线中的目的是确保信号在从驱动器元件传输到接收器时不会降级。换句话说,我们要确保出现在互连末端的信号与互连开始时注入的信号匹配。虽然信号永远不会真正经历无失真,但一些基本实践可以帮助尽可能地减少任何潜在的信号失真,以便接收器元件始终记录正确的信号。

某些标准设计实践有助于确保这一点,这些实践始于原理图输入和层堆栈设计。事实上,许多信号完整性、电源完整性和EMI/EMC问题都可以通过适当的叠层设计和电源、接地和布线的层分配来解决。其他简单的解决方案包括适当的电容器选择、阻抗计算以及了解单端走线与差分走线的限制。

什么时候应该担心信号完整性?

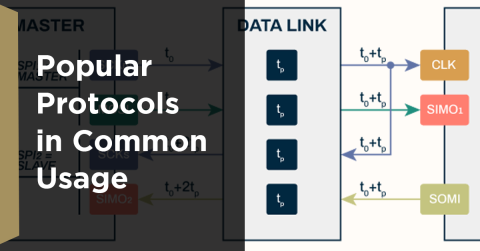

从技术上讲,任何设计都会有一些信号完整性问题,但它们一般不会干扰产品的功能或产生过多的噪声,除非您处理高速数字信号或高频模拟设计。在这些情况下,需要考虑多个问题:

- 精确的阻抗计算,防止信号反射

- 长距离互连传播过程中的损耗和色散

- 快速切换数字信号引起的串扰音

- 辐射损失过大,在EMC测试中可能表现为强烈噪音

- 由于电感过大(接地反弹),数字信号中的过冲和下冲

- 通过寄生效应耦合高频信号

- 光纤编织导致的偏斜和谐振信号损失

- 随机边缘过渡波动或SI/PI/EMI问题造成的抖动

- 沿互连长度的铜粗糙度造成的额外损耗

在高频下工作或在高速数字电路板中使用更快的开关速度运行时,这些问题更难解决。但是,为确保设计不会因这些问题而失败,可以实施一些简单的设计步骤来确保信号完整性。

从叠层开始

确保信号完整性的一个主要部分是明确定义接地并在布线期间将接地保持在重要走线附近。正确设计的叠层、电源和接地层的选择以及信号层的指定将有助于解决大多数EMI和信号完整性问题。如果叠层设计得当,还会对电源完整性产生重要而有益的影响。

下图所示为涉及交替信号、电源和接地层的典型布置示例。在本例中,该设计使用与信号层相邻的接地层来提供屏蔽、低阻抗返回路径以及定义受控阻抗线(带状线或微带线)的能力。提供具备明确定义的迹线阻抗的低阻抗返回路径以及近地信号有助于防止反射,减少EMI的辐射和接收,并提供对不同层上信号的屏蔽。

众所周知,微带线、带状线或共面布置的层厚会影响数字或模拟信号的损耗。明智地选择需要支持高速/高频信号的信号层中的电介质厚度可以解决上述损耗的一个方面。此外,为外露走线选择合适的材料和电镀材料可以降低高频损耗,例如在需要精确信号完整性的毫米波设计中。总之,这些步骤有助于确保信号在路由到互连末端时经历低损耗。

阻抗和布线的重要性

确定叠层并放置重要元件后,通过布线走线完成布局布线。数字接口和高频仿真信号中使用的信号标准将规定应遵守的阻抗要求,以确保信号的完整性并防止高速通道中出现问题。在布线过程中,需要特别注意PCB上走线的一些重要几何特性:

- 单端和差分阻抗

- 差分对的一致间距和长度匹配公差

- 使用接地过孔和均匀平面,确保整个布线的返回路径狭小

- 尽可能减少高频下的过孔过渡和过多弯曲(10 GHz)

- 在最高速度/频率布线上移除过孔短截线

前两点的设计是为了确保布线上阻抗不偏离相关信信号标准中规定的设计值。第三点确保高速/高频信号产生的返回电流具有低电感,以解决EMI和噪声耦合。最后两点解决了消除布线上任何阻抗不连续处的损耗和反射的需求。连接器和过孔等元件的输入阻抗可能会偏离所需的阻抗值,因此使用设计规则以帮助确保在设计中满足这些目标。

PCB设计软件中的布线工具可以接受您的布线要求并将其编码为设计规则,以帮助确保满足阻抗、间距、过孔数和返回路径目标。应用背钻代表了对信号完整性的成本权衡,因此应该只有在无法实施某些替代布线方案以消除背钻需要的情况下,仅应用于最快的数字信号。总之,这些措施可以解决反射引起的问题,例如眼图中的符号间干扰和不匹配传输线上的驻波。

识别信号完整性问题

信号完整性问题需要在仿真或测量中识别。理想情况下,应在设计过程中执行仿真,以帮助在创建原型之前识别任何信号完整性问题。一种常见的实践是为设计创建测试板,以便在将设计投入大批量生产之前执行测量。无论您计划如何识别信号完整性问题,都应该在将设计扩展到大批量生产之前完成这些任务。

布线期间的仿真

在设计阶段,一些更先进的ECAD软件包可以用于在一些简单的仿真中识别信号完整性问题。可以一起执行的两个标准仿真是串扰波形计算和振铃/反射波形。两种仿真都需要为PCB布局布线中的驱动元件定义逻辑系列,您可以在数据表中找到。这些仿真非常清楚地显示了互连之间的端接和间距的有效性,请参阅下文的互连瞬态响应。

在布线过程中需要检查的其他要点包括:

- 过冲和下冲

- 切换期间的上升时间/下降时间

- 并行总线和差分对中的偏差

- 返回路径连续性

可以使用针对PCB设计的高级ECAD软件包中的在线仿真工具检查这些点。设计完成布线后,应用内仿真工具可以计算这些点,以确保每个互连上的信号都在噪声容限内,并在接收元件处观察到具备所需的响应。通过在设计过程中及早识别这些问题,可以尽早解决许多信号完整性问题,理想情况下还可以消除复杂且耗时的重新设计。

信号完整性测试

尽管可以执行多项测试来评估信号完整性,但对数字设计而言最重要的两项测试是使用矢量网络分析仪(VNA)进行的S参数测量,以及使用标准测试比特流进行的眼图测试。S参数测量的时域对应的是时域反射计测量,它需要特殊仪器为互连或受测设备提供脉冲。虽然眼图和误码率计算通常使用示波器执行,但某些VNA可以生成眼图。

眼图测量和提取的误码率对于评估数字通道至关重要。它们提供一种总合测量,可以量化抖动、信号反射引起的ISI、损耗以及通过均衡进行补偿的需要。可以从这些测量中识别设计的一些简单变化,并且可以将提取的信号完整性指标与其他仿真或计算进行比较。

S参数,以及其他网络参数的仿真或测量,都是在频域中进行的。它们允许在最大可能的数据速率、传输频率、损耗或由于阻抗不匹配引起的反射方面认证设计。对于长互连,更重要的量是S21或插入损耗,因为这些通道主要由电介质、铜和辐射损耗决定。在短通道中,更重要的量是S11或回波损耗,因为在短到中等长度的通道中可能存在强烈的反射和共振。

针对SI、PI和EMI/EMC进行更复杂的仿真

一旦布局布线完成,并准备就绪,就应该首先通过更高级的仿真工具执行设计,该工具可以查看整个系统,而非只查看单个互连。这些仿真包从已完成的PCB布局布线中获取数据,并直接根据麦克斯韦方程计算电磁场。标准机械文件格式(IDX)和专业仿真数据文件格式可用于将设计数据导入外部仿真程序,从而在原型设计和生产之前识别EMI/EMC、PI和系统级SI问题。

当您使用Altium Designer®的全套PCB布局工具集时,PCB布线会更加轻松。Altium Designer中的集成设计规则引擎会在您放置走线时自动检查您的布线,让您在完成电路板之前发现并解决错误。每位Altium Designer用户均可访问Altium 365™中的专属工作空间,项目、元件数据、制造数据和其他任何项目文件均可存放在此,并与合作者共享。

我们仅仅触及了在Altium 365上使用Altium Designer可能实现的功能的皮毛。立即开始免费试用Altium Designer + Altium 365。

沪公网安备 31010502006411号

沪公网安备 31010502006411号