PDN阻抗分析和建模:从原理图到PCB布局

我们在这里讲了很多关于信号完整性的内容,但信号完整性其实与电源完整性密切相关。这不仅仅是减少电源/调压器的开关噪声或纹波的问题。在某些设计中,PCB中的PDN阻抗会对您的设计造成不利影响,从而导致电路板中的元件由于电源问题而无法按照设计工作。

这时,了解一些用于PDN阻抗分析的基本模型将起到一定的帮助作用。如果您可以为PDN阻抗建立一些合理准确的模型,则您可以为元件设计适当的去耦网络,以将PDN的阻抗保持在可接受的范围内。

为什么要进行PDN阻抗分析?

高速和高频PCB设计人员通过阅读本文即可知道答案。但是,随着技术要求的不断提高,无论是否情愿,我们所有人都将成为高速和高频PCB设计人员,因此了解PDN阻抗如何影响PCB中信号的行为就变得非常重要。不幸的是,我们在信息整合方面做得并不够好。因此,我很高兴在这里为大家做一个总结。

简而言之,您的PDN阻抗会影响电路的以下几个方面:

-

电源总线噪声。 由于PCB中的瞬态电流而产生的电压纹波。请注意,由于PDN阻抗是频率的函数,因此开关引起的电压纹波也将是频率的函数。请注意,无论调压器输出中的噪声水平如何,都会产生这些电压瞬变。

-

电源总线噪声中的阻尼。 在某些情况下,电源总线上的任何纹波都可能显示为振铃(即,阻尼不足的瞬态振荡)。如果去耦电容器的尺寸不正确,或者在去耦网络中没有考虑到去耦电容器的自谐振频率,就会出现这个问题。

-

所需的去耦水平。过去,由于电容器自谐振频率(~100 MHz)相对较低,因此使用TTL和更快的逻辑系列并不足以确保PCB中实现去耦。因此,设计人员使用层间电容来提供足够的电容,以确保实现去耦。市场上已推出更新款的具有GHz自谐振频率的电容器,它们足以在高速/高频PCB中实现去耦。

-

回流路径。您的回流电流将遵循最小电阻路径(针对直流电流)或最小电抗路径(针对交流电流)。接地网络中的阻抗会在空间中变化,并且部分取决于信号轨迹与PDN之间的寄生耦合。

-

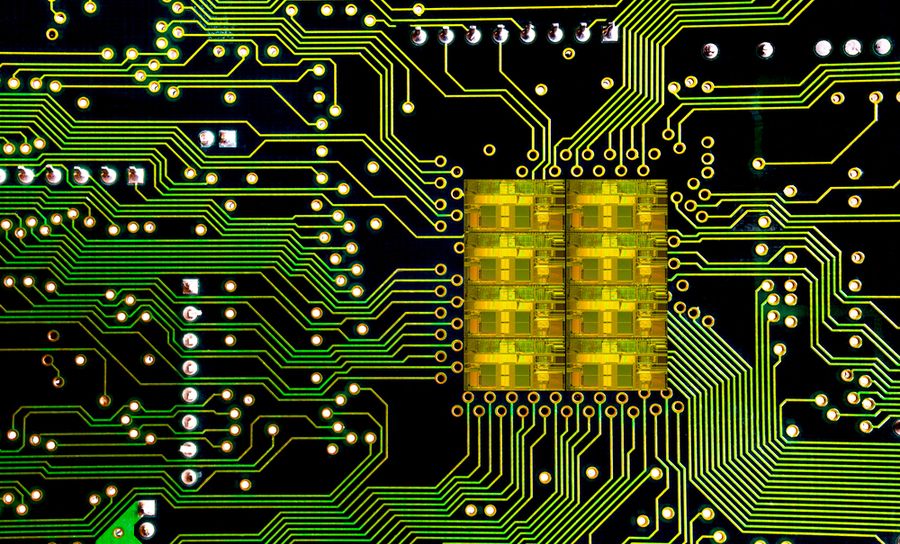

电阻压降。由于构成PDN的导体的固有电阻,供电和回流电流的直流电部分将会遭受一定的损耗。下图显示了PDN分析结果示例,说明了特定信号轨迹以下的回流电流和同一接地层中的直流电流。

-

定时抖动。由于信号的传播时间有限,因此从去耦电容器和调压器产生的电流将需要一些时间才能到达开关元件。当这些信号到达元件时,它们会干扰输出信号,从而有效地在信号的上升时间中产生一些抖动。通常,由于电源轨噪声引起的定时抖动会随着噪声强度以及调压器与元件之间的长度而增加。在长电源轨上,这可能会导致定时抖动达到几百纳秒,从而使数据去同步并提高误码率。

注意此PDN分析仪输出中的信号轨迹

PDN阻抗分析的简化模型

您可以直接从原理图为PDN的阻抗谱及其瞬态响应建模,但前提是您必须考虑到PDN中的寄生效应。在下面的模型中,您会注意到若干电路元素,但是此模型仅包含两个实际元件。第一个是您的电源/调压器,它具有一定的指定输出阻抗Z(输出),并且通常属于RL串联。第二个是去耦电容器,其理想电容为Cc1。其余的电路元素属于寄生元素。Rs和Ls值分别用于固有导体电阻和寄生电源层电感的建模。Rp、Lp和Cp元件代表了电源和接地层之间的寄生耦合(即,层间电容)。

PDN阻抗分析的简化模型。图片来源: nwengineeringllc.com

在分析此模型之前,您需要确定或估计模型中各个元素的值。去耦电容器的值很容易处理;只需从数据表单中获取所需电容器的值即可。层间电容也很容易粗略估算;只需使用载板的介电常数、重叠的接地/电源层面积以及它们在叠层中的距离,即可得到层间电容Cp。剩余的R值可以使用预期的导线尺寸计算。L值需要根据电路各部分的近似回路电感来估算;这些值通常在pH到几个nH之间。

您分析此模型的目标有两个:

-

根据频率确定右侧正负极端子之间的阻抗。这可以通过简单的频率扫描来完成。

-

检查PDN阻抗是否小于目标阻抗。请注意,目标阻抗是使用开关IC将引入PDN的电流和允许的电压纹波来计算的:

目标阻抗

-

通过添加一个与电源输出并联的电流源来检查瞬态行为(将正极端子置于Z(输出)之前)。设置电流源以提供具有下列公式所示总电荷Q的狄拉克δ函数脉冲,或提供阶跃电流。这将模拟传输到位于PDN右端的开关IC的瞬态电流。

在模拟PDN中瞬态响应时应使用的脉冲幅度

-

检查最低频率PDN谐振(即阻抗谱中的峰值)是否大于开关IC的拐点频率。这是为了在尽可能宽的频带上尽量减小纹波。

请注意,第3点旨在模拟由于下游开关IC引起的瞬态响应。如果您有10个将同时开关的IC,并且它们都向PDN引入相同的瞬态电流,那么您的脉冲幅度将要大10倍,并且您的目标阻抗将需要小10倍。检查完这三点后,您可以接着分析结果并确定可以采取哪些设计步骤来抑制PDN中的电源波动。

如何解译您的PDN阻抗分析结果

关于第1点和第2点,您要检查在时钟频率和拐点频率之间(针对数字信号)或在您将使用的相关频率范围内(针对模拟信号)的所有频率下,PDN阻抗是否均小于目标阻抗。如果PDN阻抗均小于目标阻抗,并且您已根据每个IC同时开关的情况计算了阻抗,则您的PDN可能会按预期工作,且不会导致任何信号完整性问题。

如何处理第3点的结果,则取决于PDN中的瞬态响应是否显示为欠阻尼振荡。如果瞬态响应欠阻尼,则需要使振荡进入临界阻尼或过阻尼状态。这要求使用较大的去耦电容器,或使用有效串联电感较低的电容器。去耦电容器的尺寸应能提供上文列出的脉冲电荷,但您当然也可以尝试使用更大的去耦电容器,以改变实现最低PDN谐振的条件,从而使瞬态响应过阻尼或小到不可计量。

尽管第4点中的目标并不一定能够实现,但这并不妨碍您进行尝试。即使您无法达到这一设计目标,如果PDN谐振时的阻抗仍然小于目标阻抗,并且在相关带宽内只有一个PDN阻抗谐振,那就仍然不会有问题。如果在相关带宽内有多个阻抗谐振峰值,那么您可能会遇到麻烦,因为瞬态电流遇到的总阻抗大约是峰值阻抗的总和,而从现在的情况来看,这一总阻抗可能会超过目标阻抗。

除了上文提到的去耦电容器大小和自谐振问题外,第3点的结果还应该说明了为什么层间电容被列为1 ns或更快速逻辑IC(例如ECL)正确去耦的条件。除了使用具有非常高的自谐振频率的超大去耦电容器(现已在市场上出售)之外,将接地层和电源层放置在相邻层上的做法一直是在PDN中提供所需去耦等级的唯一方法。请注意,无论您是使用多个电容器来增加层间电容还是去耦电容(参见前段中的链接文章),只要该电容足够大,都会导致瞬态响应进入过阻尼状态,从而有效地消除瞬态响应。

使用怎样的管芯和封装结构?

但愿精明的设计人员已经注意到,上文所述分析中,并未考虑到封装和管芯结构对阻抗的影响,因为它们均内置于PDN中的载荷中。但是,由于它们会产生电容性和电感性寄生效应,因此在PDN中,也需要考虑到这些因素。

具有封装管芯结构寄生效应的PDN模型

借助 Altium Designer®中功能强大的PCB设计和分析工具,您可以从各个方面对原理图和布局进行分析,并防止在复杂PCB中出现信号完整性问题。这些工具建立在由统一规则驱动的设计引擎基础上,使您可以在整个设计过程中执行重要的DRC检查。您还可以通过单个平台,获得全套制造规划和文档功能。

现在,您可以下载Altium Designer 免费试用版 ,详细了解业界最佳的布局、仿真和产品规划工具。 立即联系我们 了解更多信息。

沪公网安备 31010502006411号

沪公网安备 31010502006411号