具有JESD204接口的ADC/DAC组件

许多较简单的系统将包括一些混合信号功能,有时这些功能通过ADC内置于主控制器中。为了获得更准确或更快的采样,通常会使用外部ADC,包括在需要非常快速采样或以GSps操作速率进行合成的系统中。当这些功能需要跨多个数据转换器实现,而所有这些转换器可能都以非常快的采样率运行并与参考振荡器同步时,会发生什么情况?

对于具有多个数据转换器的高级混合信号系统,我们不能依赖于更简单的源同步总线或通用串行接口。幸运的是,JEDEC开发了一种专门针对这种情况的接口:JESD204接口。该接口旨在简化使用LVDS通道时与多个数据转换器强制同步相关的布线困难,而不会将采样率限制为低值。

本文将概述在使用多个ADC和/或DAC并且采样率快时,JESD204接口中存在的重要设计要求。将这种类型的系统联系在一起的关键是主控制器,这是一个将接口从供应商IP实例化的FPGA。

关于JESD204接口

如果需要,ADC和DAC可以以非常高的采样率运行,轻松达到GSps范围(每秒千兆次采样)。这是一个非常高的采样率,适用于获取RF信号(使用ADC)或以RF重复率生成波形(使用DAC)。当系统使用单个数据转换器操作时,可以使用快速串行接口向系统主控制器发送/接收数据。然而,当系统中存在多个数据转换器时,通常需要同步,而这很难通过像LVDS这样的串行接口强制执行。

这就是JESD204接口发挥作用的地方。这个由JEDEC发布的标准化接口,旨在替代数据转换器之间以及每个数据转换器与系统主机之间使用LVDS链接。该标准的最新修订版(Rev C,或JESD204C)定义了一种串行协议,可用于同步多个以高采样率运行的ADC和/或DAC。可以同步的主要功能有信号采样、合成和跨多个数据转换器的时序。

因为JESD204接口是作为ADC/DAC的LVDS替代品开发的,因此值得比较这两个接口在多个数据转换器中的实现:

支持JESD204接口的ADC/DAC组件将直接在芯片中构建I/O块,而系统主控制器将在FPGA互连织物中实例化接口。为了确保系统同步,具有JESD204接口的ADC/DAC将包括专用的SYNC/SYSREF引脚,以支持来自JESD204C或JESD204B设备的时钟触发。

JESD204的优势

从上表中可能不明显,但JESD204接口对多个数据转换器的主要优势是其定时方法。一个符合JESD204的系统的拓扑结构涉及通过其参考振荡器分配在所有设备上进行同步采样,如下面的块图所概述。这使得所有数据转换器与主控制器的时钟同步,因此采样/合成的时钟与系统主机的时钟相同。

采样/合成在单个数据转换器中通过SYNC引脚触发,然后驱动数据从单个数据转换器流向主控制器。数据流有自己的嵌入式时钟,因此接口可以自动消除两个数据流的偏移。这就是为什么每个数据转换器的差分数据线不需要与JESD204接口的长度匹配。从技术上讲,可以在使用LVDS的一组级联ADC/DAC中添加相同类型的消偏功能,但这将需要在软件或逻辑中计算消偏。

如果你观察时钟源、主控制器和数据转换器之间的时钟/同步分配,对于在主处理器中实例化的给定JESD204接口,将会有一些允许的偏移预算。接口中最长和最短跟踪之间的偏移不匹配预算必须在接口的定时方案可以补偿的某个最大偏移值内。如果在偏移预算内操作,接口将能够检测到DATA通道上结果输入数据流之间的不匹配,并且可以在逻辑中补偿消偏。这产生了采样信号之间的真实相位差异。

多个JESD204 ADC/DAC与多通道组件

如果你熟悉ADC/DAC,那么你应该知道这些组件通常具有多个输入/输出通道用于信号获取/生成。鉴于这是事实,公平地问一个问题:与使用单个多通道ADC/DAC相比,使用像JESD204这样的接口的单独ADC有什么优势?

使用多通道ADC与单个ADC相比存在的一些挑战包括:

-

通道间串扰

-

增益、偏移和动态范围匹配

-

交错采样

-

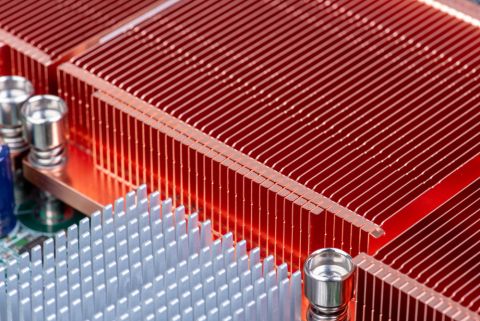

功耗和热量

多通道DAC中可能存在相同的挑战。这些组件可以在单个芯片中提供数十个通道,因此在需要时它们确实能够提供非常高的密度。然而,这种设计自由伴随着一些条件。注意,有些多通道ADC包括JESD204接口。下面概述了每种方法的优势。

本质上,具有单一可控参考的多通道ADC可能无法提供获取或生成不同类型信号(在偏移、噪声水平(分辨率、动态范围和/或增益)方面的灵活性。通过使用独立的ADC,可以独立设置采样/合成特性,尽管这确实会增加每个接口的组件数量。因此,主要的权衡是较低的密度。然而,这种较低的密度是减少串扰所必需的。

重要的考虑因素来自于频率函数的串扰。在射频频率下,通道之间的串扰会比低频时更加强烈,这种串扰会在使用同时采样的ADC中反映在各个通道之间。解决方案将是使用交错采样,但现在你完全失去了精确检测通道之间相位偏移的能力,因为它们不是同时被采样的。这也应该说明了对于多个数据转换器,兼容JESD204接口的优势:在射频频率下精确的相位确定。

兼容JESD204的组件示例

市场上有许多组件提供快速采样率,具有JESD204B或JESD204C接口。带有JESD204C接口的新组件仍在上市,下面将介绍其中的一些示例。

Analog Devices AD9207BBPZ-6G

Analog Devices的AD9207BBPZ-6G是一个双12位ADC,最大采样率达到6 GSps。这个组件的数据流接口可以在JESD204B或JESD204C之间选择,最大数据流速率达到接口标准允许的最大值15.5 Gbps(JESD204B)或24.75 Gbps(JESD204C),跨越8个通道。为了控制输入共模噪声,这个双组件使用1.475 Vpp差分输入接口,高频采样时钟通过片上PLL生成。采样分辨率也可以在8、12、16和24位之间选择,取决于JESD204B或JESD204C模式。这个组件的新版本,AD9213BBPZ-6G,提供了许多相同的功能,但采样率可达10.25 GSps。

Texas Instruments ADC12QJ1600AAVQ1

Texas Instruments的ADC12QJ1600AAVQ1是一个快速ADC,最大采样率达到1.6 GSps,采用非交错架构。该组件是一个四通道ADC,带有JESD204C接口,支持2到8(四/双通道)或1到4(单通道)serdes通道,最大数据率为17.16 Gbps(64B/66B或8B/10B编码)。全功率-3 dB输入带宽为6 GHz,为FMCW激光雷达或其他基于脉冲接收的系统提供平坦的频率响应。这个输入带宽也适合L和S波段的直接射频采样。

Texas Instruments DAC38RF86IAAVR

德州仪器的DAC38RF86IAAVR是一款与JESD204兼容的DAC,具有14位分辨率和最高9 GSps的采样率。该组件提供直接合成基带信号或用于雷达或无线通信等应用的广播信号。该设备提供单端输出,并集成了平衡器。通过集成的NCO实现内部时钟,允许使用低频参考振荡器。为了帮助实现这些组件的JESD204接口,德州仪器提供了用于FPGA开发的IP。

支持数据转换器的其他组件

在非常高频率下操作的数据转换器系统是高度专业化的,它们可能需要信号链中的许多其他组件以确保准确的信号采集。这些组件包括具有模拟接口的数字接口,因此PCB布局中使用的实践需要这些板块之间的隔离,这有时会激励在一些网络上使用滤波器或额外的串联终止。

设计师可能需要支持级联信号采集/合成的其他组件包括:

想要找到像JESD204兼容的ADC和DAC这样独特组件的设计师,可以通过Octopart的高级搜索和过滤功能找到所有他们需要的混合信号组件。只有Octopart提供高级搜索和过滤功能来帮助买家找到组件以及最新的分销商定价数据、零件库存和零件规格。查看我们的集成电路页面以找到您需要的组件。

通过订阅我们的新闻通讯,随时了解我们的最新文章。

沪公网安备 31010502006411号

沪公网安备 31010502006411号