差分对阻抗:使用计算器设计PCB

我在高中时上过各种各样的计算机课程,并且始终有一个疑问,那就是为什么以太网电缆中的导体要相互缠绕在一起?我不知道原来这是一种简单的设计方法,可以确保信号在不互相干扰的情况下抵达目的地。有时,复杂问题的最佳解决方案实际上也是最简单的解决方案。

差分对布线不只局限于以太网线缆;它也是高速PCB中的关键布线和设计技术之一。电路板设计人员通常从单端走线而不是差分对走线的角度来讨论传输线阻抗,但是清楚地理解和计算差分对阻抗对于确保整个电路板的受控阻抗至关重要。电抗、电感和阻抗等因素通常可以归结为一个简单的解决方案。

差分阻抗何时起到重要作用?

高速/高频PCB中的阻抗失配会严重破坏信号。当单端走线中存在明显的阻抗失配时,会出现诸如由于产生信号共振而导致的振铃之类的问题。这同样适用于不同的对;但与具有高输入阻抗的负载相连的端接对是个例外(例如,LVDS)。就像单端阻抗一样,当走线表现为差分传输线时,差分对阻抗具有重要意义,具体取决于给定走线上的传输延迟。

在信号上升时间非常短的情况下,差分对阻抗应与源和负载元器件匹配。除非走线与其上游和下游元器件之间的失配很严重,否则通常不需要进行阻抗匹配。您需要通过查看 信号标准所允许的阻抗失配来确定临界长度,当超过该临界长度时,需要执行阻抗匹配。对于数字信号,这一有效长度可以转换回上升时间;对于模拟信号,可以转换成该对长度的一部分波长。

如果信号上升时间少于沿走线的往返传输延迟的两倍,则应将走线视为传输线。如果您想要保守一点,那么当带宽扩展到GHz范围内时,应始终在高速和高频PCB中进行阻抗匹配,这是因为信号波长/传播延迟长度将在几厘米的数量级上。如果走线的传输延迟大于上升时间或振荡周期界定的临界往返传输延迟的10%,那么将走线视为传输线是一种更加保守的行业标准规则。在不确定的情况下,匹配阻抗以防止信号反射问题的做法更为安全。

差分对中的耦合,可以决定差分阻抗。

对于差分对阻抗,通过一些简单的公式,可以仅使用特征阻抗和耦合强度来估算差分对的阻抗(未连接任何负载时)。 与Ben Jordan一起观看此次网络研讨会, 以了解有关计算的更多信息,并查看用于差分微带线的简单公式。

对于数字信号和宽带模拟信号,在计算差分阻抗时,需要考虑到信号的频谱。对于数学家来说,数字信号中的频率内容可以表示为模拟频率的总和,并且由于 电介质中的色散,数字信号的每个模拟部分的介电常数都将略有不同。这意味着搭载数字信号的差分对中的耦合会在数字信号或宽带模拟信号的整个频谱范围内变化。

这些事实使差分对阻抗和单端走线阻抗的计算变得相当困难,除非您拥有一个定义电介质中色散的模型。如果您不喜欢求解耦合型偏微分方程组(参见Telegrapher的方程式),那么正确的差分阻抗计算器可以帮助您确定用于所需差分阻抗值的正确走线宽度、间距和与参考面的距离。

差分阻抗计算器

与多个差分阻抗计算器一起使用时,需要事先知道走线的介电常数。这需要用到另一个根据您的特定几何形状定制的阻抗计算器,或者您需要手动计算出PCB基板中每个频率的介电常数。获得介电常数并选择走线排列后,就可以开始运行计算以确定正确的几何形状了。您可以使用几何参数,直到达到所需的阻抗水平,或者可以约束几何形状,并将计算出的阻抗值用于PCB中的阻抗匹配。

大多数计算器返回的差分阻抗值等于每条走线的阻抗之和(包括耦合造成的阻抗)。将该值除以2可以得到每条走线的奇模阻抗值。在极限情况下,将走线之间的间距设置为非常大的值会导致走线的阻抗收敛到具有相同几何形状的单端走线的特征阻抗。

许多在线差分阻抗计算器的一个缺点是它们不允许您将阻抗作为频率的函数来计算。一些RF计算器仅在特定频率(通常为2.4 GHz)上执行计算,否则它们会要求您必须指定您选择的单个频率。差分对阻抗及其S参数与频率有关,这是由于色散(如上所述)以及负载分量对中等长度走线中的输入阻抗的影响所致。我在网上看到的所有差分对阻抗计算器都没有考虑到这些事实。他们只是简单地计算隔离差分对的阻抗。

对于复杂的阻抗匹配,输入阻抗很重要,因为这是信号进入差分对时遇到的阻抗。在频域中,由于谐振,输入阻抗谱在中等频率范围内出现最小值,然后随着频率的降低和升高,阻抗逐渐增大。在时域中,在特定的振荡周期/上升时间会出现一个最小值,然后随着信号周期/上升时间增加到往返延迟时间,单调阻抗逐渐增大。此时,功能强大的设计软件和出色的仿真工具将变得尤为重要。

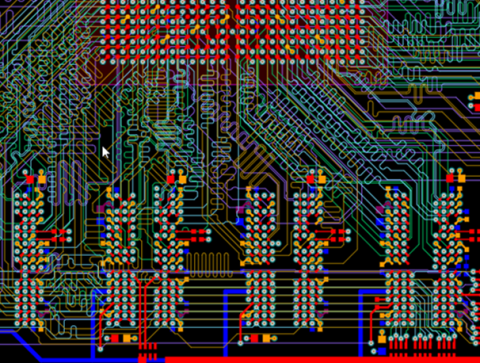

使用集成场求解器控制差分对阻抗

如果您的布线工具是以集成场求解器为基础构建的,那么您将能够为走线定义单端或差分阻抗要求。创建布局布线时,您还可以对照复杂的阻抗公差检查差分对布线。您无需手动计算走线尺寸或间隔;这些将在您创建电路板叠层时根据频率自动确定。

出色的PCB布局软件,诸如Altium Designer,可以使您在接下来的高速或高频设计中轻松完成差分对的布局。ActiveRoute工具、xSignals工具和集成场求解器可以帮助您通过受控阻抗轻松实现差分对布线。您将拥有必要的工具帮助您分析和防止由于阻抗失配而引起的信号问题。如果您有兴趣了解更多关于Altium Designer的信息,可立即与Altium Designer负责人联系。

沪公网安备 31010502006411号

沪公网安备 31010502006411号