Landless Vias

One persistent myth is that PCB vias MUST have annular rings. I thought this for many years until our Japanese partners introduced us to landless vias. We said, “You can’t do that, the vias have to have lands!” They replied, “Try it out and test it?” So, we created a test vehicle and tested thousands of vias with various diameters against numerous annular ring vias. Guess what? They were right!! As the annular ring got smaller, the failures occurred earlier until we got to landless, then they jumped to 10 X fewer failures.

Not understanding this result, the PhDs of HP Labs went to work and came up with an explanation (published in one of the IEEE conferences). This was so radical a discovery that HP made the data, explanations and results proprietary—a company secret.

Introduction

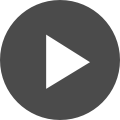

I saw my first landless via multilayer while visiting NEC at Toyama, Japan back in 1985 [1]. They were an enormous automated facility making Japanese telecom and mainframe computer boards, kind of like IBM and Western Electric rolled into one. NEC was using the liquid, electrophoretic, positive-acting photoresist process with panel-plating. I wouldn’t see another landless via multilayer until our Japanese partner (OKI) introduced it to us in 1988. OKI was using the landless vias to achieve higher density without having to pay the extra costs of finer lines. They knew about the higher reliability that resulted, the had done their own testing (see Figure 1) but were after the higher routing density. These vias are seen in Figure 1 and it allowed them to route five traces between 0.100 in PTH centers.

An excellent explanation for the high reliability of landless vias is found in the latest PC Handbook (7th ED) in Chapter 60, page 1307 and a recent PCB007 magazine.[2]

Figure 1: a &b. Typical landless vias on a Japanese multilayer from around 1985 c. Modern landless made in N. America in the 2000s [0.010 in (0.25mm) and .004 in (0.1mm) traces] created with the liquid, electrophoretic, positive photoresist from PPG

Landless Via Fabrication Processes

There are numerous patent applications about landless vias. All require laser sculpting of the via or pinpoint laser exposure for the imaging. None of these have ever entered production. The two that have been used in high volume production are listed here, with two additional techniques that appear to be very practical.

HP Process Learned from the Japanese

The Japanese process for making landless vias is very simple, but anyone I talked to never figured it out until I explained the process. It is a true example of “thinking outside the box”:

-

Whatever your registration tolerances are, then reduce the artwork land opening size by that amount. When using dry film photoresist. The DF will now extend beyond the wall of the drilled hole.

-

Two things will happen with this arrangement:1. the plating bath will be forced to throw into the hole improving the distribution; 2. There will be no land except where the trace enters the hole.

-

After stripping and etching, there will be landless vias with the trace dropping into the barrel of the PTH or blind via.

-

This process does not work for panel plating. Then you must use the next process like NEC.

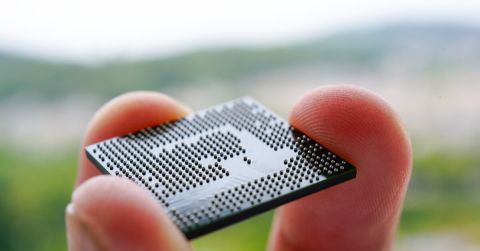

Figure 2. More landless vias including three more examples of ‘invisible vias’. A. Laser drilled 0.1mm blind via in a 0.1 mm trace; b. two landless vias on a 0.008 in (0.2mm) TH; c. The one view shows 0.2 mm pitch traces with 0.1 mm landless vias and the proportional size if there were 0.2mm, 0.4mm or 0.35mm lands on the vias; d. 0.1 mm trace in a plasma-etched, 0.2mm blind via.

Positive Liquid Electrophoretic Photoresist

NEC were using a positive electrophoretic photoresist from Nippon Paint, evolved from the electrophoretic paints used on automobiles. A more recent photoresist and process came from PPG and is documented in a paper by Patty Goldman of PPG and Tim Schmidt of Compunetics.[3] The positive acting photoresists have many properties that can be very useful. The most useful is multiple exposure and developing, its resistance to plating especially Ni-Au and etching, its fine-line resolution [down to 10 microns (0.4 mil)] and its insensitivity to dust and clean-room debris. The coating process is relatively simple:

• Clean panel

• Coat for 60 to 90 sec at 60V~100V (voltage will determine finished thickness)

• Rinse

• Bake dry

The panels are now ready for exposure or transportation. Coated-exposed and developed panels are shown in Figure 1.

Perfect Registration

Now with the advent of Direct Digital Imaging (DDI) and board scanning, it is possible to have perfect registration on both sides of a board. A DDI unit I tested has nine cameras that scan a panel as it enters the machine from both sides. Then, as it starts to expose each side, the artwork is modified on-the-fly so that each land is perfectly registered to its hole. Without high-speed computers, scanners and the new software, this was impossible before.

Novel Russian Technique

At a recent PCB West Conference, I had a conversation with a Russian PCB fabricator. It seems the Russians also used landless vias after they saw it on Japanese computers. The Russian process was novel, and I wish I had thought it up! They used the property of dry film photoresist’s sensitivity to oxygen. When they laminate the dry film to the panel, they have a shroud around the unit filled with oxygen. Oxygen is trapped in the holes by the dry film. They expose the panel to their normal artwork (but there are no lands for traces that will interconnect to the landless vias. They then do a short 100C bake of the panels, remove the cover sheet on the dry film and develop normally. The oxygen and heat have polymerized the dry film from the inside at the same diameter as the hole. Thus, when developed, the via has perfect dry film registration and is landless.

If you’re running out of space, give it a try!

Would you like to find out more about how Altium can help you with your next PCB design? Talk to an expert at Altium or learn how Altium Designer® offers the best toolset for PCB via creation in PCB design. Altium provides a tool that gives you editors, templates, rules definition, and libraries to address properties for assignment to your vias.

References

-

Hirai, Osamu, The Development Of Advanced Cu-Plated Through Hole PWB With Landless Vias, Printed Circuit World Convention IV, Session 58, June 5, 1987, Tokyo, Japan

-

Holden, H, “Against the Density Wall: Landless vias may be the answer”, PCB007, June 2016

-

Goldman, Patty & Schmidt, Tim, New Design Applications Made Possible by Utilizing a Positive Acting Electrophoretic Photoresist., IPC's 2002 Designers Learning Symposiums, Dallas, TX (May) and Toronto (October)

沪公网安备 31010502006411号

沪公网安备 31010502006411号