Overview of the PCIe 6.0 Standard

Just as you get used to PCIe 5.0, they decide to release another standard!

Ever since PCI Express was introduced as a replacement for the original PCI specification, the PCI-SIG standard group has doubled the bandwidth approximately every 3 years. The cadence of performance changes and bandwidth increases suddenly hastened around the time of PCIe Gen4, with the current time between generational releases of about 2 years. Since its introduction, PCIe continues to be a standard that enables high-bandwidth access to specialized peripherals.

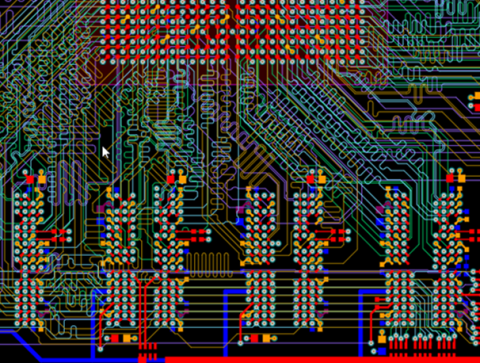

The newest iteration of PCIe is Gen6, or PCIe 6.0. PCIe 6.0 brings a doubling of channel bandwidth through introduction of PAM-4 as the signaling method in high-speed differential channels. This signaling method is a first for PCIe, and it’s an important enabler of the doubled data rate we see in the current standard. In this article, I’ll run over the important points in the standard and what PCB designers can expect when designing these channels.

PCIe 6.0 Overview

The main performance characteristics in PCIe 6.0 channels are summarized in the table below. These specs are current as of the final publication of the PCIe 6.0 standard by PCI-SIG in January 2022.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PAM-4 and Interoperability

As mentioned above PCIe 6.0 uses PAM-4 links, while PCIe 5.0 and earlier specifications use NRZ. Although the signaling standards are still different, backward compatibility is ensured through the PCIe 6.0 device operating a PAM-4 link with two effective signal levels. Shifting to PAM-4 with a 4-tap FIR filter for distributed feedback equalization aids signal recovery at the receiver to help compensate for high-frequency loss with adjustable DC gain.

Forward Error Correction (FEC)

The transition to PAM-4 encoding provides for a significantly higher BER compared to NRZ. FEC is used in Gen6 to offset the higher BER value in routed channels. In PCIe 6.0, the FEC mechanism works in conjunction with cyclic redundancy check (CRC) with a latency target below 2 ns. Just for comparison, some signaling standards have FEC latency of greater than 100 ns, which does not meet bandwidth and latency demands of PCIe technology.

FEC with PAM-4 signaling also helps to increase the range of a PCIe 6.0 lane so that it is essentially the same as in a PCIe 5.0 lane. This is because the data rate in the channel is increased, but the signal bandwidth (Nyquist frequency) does not increase.

Flow Control Unit (FLIT) Encoding

PCIe 5.0 and earlier generations used an embedded clocking scheme with fixed 2-bit encoding. Packet efficiency in PCIe 6.0 is higher through elimination of the 128B/130B encoding and overhead from data link layer packets (DLLP). FEC and CRC both require a fixed FLIT size to apply error correction, so PCIe 6.0 uses FLIT to simplify data management and error correction.

Market Drivers for PCIe 6.0

PCIe is a major upgrade from the PCIe 5.0 standard, but it is not something you will find in every embedded device. Data transfer rates of 64 GT/s per lane is something only the most advanced embedded systems will ever need. The highest bandwidth embedded device for sensor fusion I’ve ever worked with operated with 28G and 56G channels, and those systems are uncommon outside of mil-aero and data center environments. Although those types of systems exist in some of the most advanced applications, they are not the main market drivers of the need for PCIe 6.0.

So what’s driving the need for this higher bandwidth to reach peripherals? Two of the main drivers are the computing environment in modern data centers, primarily driven by the large cloud services providers. Some of the primary applications include:

- AI in the data center, which aids web applications or that would be accessible as a service by embedded devices and applications

- Access to the highest bandwidth networking protocols (800G Ethernet)

- Introduction of SSDs, where newer PCIe generations are relied on for access to storage resources in data centers and edge servers

A 16x PCIe 6.0 interface will provide 128 GB/s data rate across the entire interface; when aggregated and compared with 800G Ethernet, we see that 16x interface can provide the 800 Gbps throughput needed for this advanced networking standard. Thanks to the bandwidth double mechanism through PAM-4 signaling, PCB design with PCIe 6.0 will follow many of the same high-speed PCB layout and routing techniques used with other high-speed standards.

When you need the most powerful layout and routing tools for PCIe 6.0 links, use the PCB design tools in Altium Designer®. When you’ve finished your design, and you want to release files to your manufacturer, the Altium 365™ platform makes it easy to collaborate and share your projects.

We have only scratched the surface of what’s possible with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.

沪公网安备 31010502006411号

沪公网安备 31010502006411号