RISC-V 处理器和 SoCs 用于嵌入式系统

每个微处理器都建立在指令集架构(ISA)之上,该架构定义了用于执行数字数据计算操作的高级功能。ISA是CPU的核心组件之一,定义了软件如何与硬件通信。它基本上以机器能理解的方式定义命令,通常包括内存操作、数据处理、算术操作、逻辑操作和控制流操作的指令。ISA还定义了如何存储、编码和访问指令。

过去二十年中占主导地位的ISA包括x86、x64和ARM,这些架构推动了个人和嵌入式计算的采用,达到了我们今天看到的水平。虽然ARM是最常用的处理器架构之一,但半导体行业正在接受一个新的开源竞争者。这种替代架构是RISC-V(发音为“风险五”),它已被开源社区和半导体供应商作为ARM和x86/x64架构的替代方案所接受。

虽然我们不期望英特尔的x86/x64或ARM架构很快就会消失,但RISC-V提供了一个引人注目的开源替代方案。现在一些半导体供应商在他们的FPGA中支持RISC-V实现,开源社区也以供应商IP和库的波浪来响应,以帮助加速开发。在这篇文章中,我们将看看半导体供应商最近推向市场的一些基于RISC-V的产品。

RISC-V是什么?

RISC-V ISA是一个开源的ISA,可用于定义在微处理器核心中实现的核心低级数字数据操作。该规范使用一套与32位硬件实现兼容的49条指令。字宽可以使用64位与一套14条扩展指令,或理论上高达128位。作为一个开源规范,主要指令集和可选扩展可以被自定义、移除或完全重写,以提供用于新芯片中的定制化或高度特定的处理器架构。

自从2010年(在伯克利的Par Lab)开始RISC-V开发以来,RISC-V的创造者们接着创立了SiFive,一家处理器核心IP公司。该公司提供了基于RISC-V的第一个完全开源的处理器核心架构。该架构可以用作设计实现RISC-V ISA和任何附加用户功能的数字逻辑架构的基础规范。

为什么基于RISC-V构建?

在 RISC-V 上构建自定义应用处理器为开发者提供了一条优秀的路径,无论是在定制硅片上构建新处理器,还是在 FPGA 上构建可重配置处理器。在 FPGA 上使用 RISC-V 进行逻辑开发带来了自己的好处,这得益于 FPGA 平台的可定制性和可重配置性,以及它们的高计算密度。对于需要超过实时操作系统(RTOS)的嵌入式应用,RISC-V 核心可以被移植以支持 Linux 发行版。

RISC-V 处理器和 IP

RISC-V 开发者可以通过两种可能的方式使用指令集及其硬件实现:在新的芯片设计上开发自定义逻辑设计,或在 FPGA 中实现专用逻辑。行业刚刚开始使用 RISC-V 作为微控制器设计的核心架构,但这些组件尚未大规模可用。

目前,能够支持 RISC-V 的商业可用处理器范围限于 FPGA,其中 RISC-V 通过供应商 IP 得到支持。就目前而言,在 FPGA 上构建是系统开发者的一个绝佳选项,无论是从原型设计的角度,还是从设计专为重计算工作负载而大幅简化的定制应用特定硬件的角度。

Microchip PolarFire

Microchip 的 PolarFire 平台是该公司基于 RISC-V 的旗舰 FPGA 平台,其中一块现成的处理器直接从 FPGA 互连织物构建而成。PolarFire 产品线包括多个组件和部件号,所有这些都旨在以最低功耗实现嵌入式应用中的高计算密度。这款 FPGA SoC 可以使用 Libero SoC Design Suite 进行大量定制,且 PolarFire 平台可使用核心 IP。就硬件能力而言,系统可以支持 12.7 Gbps 收发器和 PCIe 2 I/O。

Efinix Trion 和 Titanium

Efinix 是一个较小的半导体供应商,但他们已经在其供应商 IP 中采用了 RISC-V,推出了 Trion 和 Titanium 产品的两款 SoC 产品。

Sapphire SoC - 这种 RISC-V 实现是一种用户可配置的实例化,具有可选的内存控制器(DDR 或 HyperRAM)和多个接口(最多 32 个 GPIO、3 个 I2C 主控、3 个 SPI 主控和 3 个 UART)内置于设备核心。

Edge Vision SoC - 这个库旨在用于嵌入式视觉应用,它包括此类应用领域的标准接口。可以使用开发者工具向此 IP 添加额外的用户功能,如专用的 DSP 块或数据操作。

为了帮助用户开始使用新平台,两个产品线都提供了开发产品,例如用于视觉应用的 Trion T20 MIPI D-PHY/CSI-2 Dev Kit。

Xilinx 和 Bluespec

Bluespec Inc.,作为Xilinx的官方开发合作伙伴,现在支持在Xilinx FPGA上实现32位RISC-V核心。这个SoC IP针对的是需要在FPGA上运行Linux的单处理器核心应用程序。RISC-V RV32IMAC SCL支持RISC-V基础整数指令(I)、整数乘除(M)、原子(A)和压缩指令(C)、单双浮点指令(FD)。用户可以使用Vivado IDE中的标准开发工具集在Xilinx FPGA上实现Bluespec RISC-V 32IM核心IP。

使用像Xilinx这样的主要供应商的硬件的好处是,为构建嵌入式应用程序提供了大量的开源支持和开发产品。Xilinx的广泛IP组合可以与在RSIC-V中定义的核心逻辑架构一起使用,以构建定制的硬件实现。例如,SiFive的Freedom E310核心IP可以使用Arduino IDE编程到Digitlent的Arty A7开发平台上。

即将上市的其他产品

其他公司最近也宣布了关于在新半导体产品中使用RISC-V核心的产品公告。这些产品旨在更接近于应用处理器,仍然通过嵌入式应用程序提供一些通用的可编程性。一些最近的产品公告包括:

-

Renesas Application Specific Standard Products (ASSPs),一系列基于RISC-V的产品,旨在将通用处理与应用特定性结合起来。

-

Picocom PC802 5G NR SoC,一个针对5G NR小型基站的应用特定处理器,通过O-RAN Open Fronthaul eCPRI或JESD204B与无线电单元接口。

-

Intel现在将通过其新的代工服务部门支持RISC-V,允许无晶圆厂公司创建与Intel的硅处理能力兼容的设计。

RISC-V开发的更多资源

芯片设计是一门艰难的学科,但使用像RISC-V这样的开源指令集作为开发框架是加速芯片架构设计的好方法。对于逻辑设计师来说,挑战在于创建代表RISC-V规范中定义的指令的逻辑电路。对于微控制器或MPU来说,这是一个艰巨的任务,需要大量的经验;这通常不是设计师能够独自完成的事情。

然而,对于FPGA来说,有许多RISC-V实现可以用来快速构建一个高度可扩展的架构,该架构整合了自定义用户功能。这是供应商工具和开源社区花了大量时间构建的东西,现在有许多RISC-V核心可以在FPGA开发中使用。要开始,请查看一些这些GitHub仓库:

这只是可用资源的一小部分,你会在GitHub上找到更多对各种FPGA有用的开源仓库。此外,对于任何对在ISA上构建感兴趣的FPGA开发者,RISC-V International推出了一个RISC-V培训合作伙伴计划。开发者可以更深入地了解开放合作的好处,并扩展他们对RISC-V的知识。

RISC-V架构的一个重要优点是它可以被修改并在开放市场上销售。无晶圆厂半导体初创公司现在基于RISC-V ISA提供其核心IP,以类似于ARM的商业模式授权给其他公司。同样,公司正在使其供应商IP可供购买,并用于主要半导体制造商的FPGA中。随着这些基于RISC-V的组件进入市场,我们可以期待它们为高级应用提供高水平的特异性。

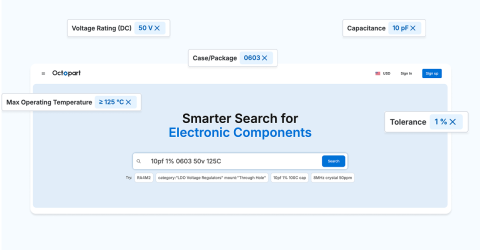

当你准备开始选择你的FPGA、可编程SoC和新系统的其他组件时,请确保使用Octopart中的高级搜索和过滤功能来找到他们需要的所有高级组件。当你使用Octopart的电子元件搜索引擎时,你将能够访问最新的分销商定价数据、零件库存和零件规格,而且它都是在一个用户友好的界面中免费提供的。看看我们的集成电路页面来找到你需要的组件。

通过订阅我们的新闻通讯,随时了解我们的最新文章。

沪公网安备 31010502006411号

沪公网安备 31010502006411号