是否应该在PCB电源层中布线信号?

设计师经常询问我有关信号完整性和电源完整性等方面的问题,而最近的这个问题迫使我(再次!)思考平面和覆铜附近的一些基本布线实践。以下是我最近在LinkedIn上收到的(已改述)问题:

我想知道您对在PCB堆叠的同一层上混合信号/电源的看法。是否可以将信号迹线与电源层布置在同一层?我发现一些堆叠指南表明这没问题,但未提供可靠的建议。

我们再次发现一个长期存在的设计指南的极佳示例,但没有足够的背景。这个问题的简短答案是“是”,在某些情况下可以这样做。这种做法很常见,我们在客户电路板上这样做,没有任何阻抗问题、EMC问题或这些产品上的直流功率损耗,因为堆叠设计正确,并且我们考虑到如何正确布线设计。不过,在电源层上布线信号或在信号层上布线电源轨时需要考虑多个维度。困难来自于电路板中的电源完整性、受控阻抗和直流电源分配。

如何在PCB电源平面层中布线信号

在开始切割附带迹线的PCB电源平面层之前,您需要考虑以下方面的设计要求:

- 电源层电流容量

- 低速与高速信号和阻抗

- 如果将平面用作参考层,则返回路径

让我们更详细地看一下其中的每种用途。

电源层电流容量

每当您设计电源层时,它都会具有一些定义的载流容量,该载流容量与构成平面层的铜尺寸有关。如果您开始通过高功率平面进行布线,则会将平面分割成多个部分,并且每个部分的电流容量将低于统一平面层的电流容量。此外,如果电源层的形状非常复杂,您最终可能会创建一个具有高电流密度的漏斗,该漏斗会变得相当热。您可以在PDN分析器仿真中可视化处理类似的效果(有关示例,请参阅本文)。

弥补电源层布线的一种解决方案是在相邻层上使用并行运行的其他电源层。在这种布置中,您实质上是将电流分离到两个并行平面,这将有助于确保不会超过任何一个平面部分的电流容量。对于大多数低功率设备来说,一般不需要担心这个问题。但是,如果您拥有一个高功率系统,则可能无论如何都需要执行此操作,以便系统可以提供足够的功率而不会变得太热。这样做的一个常见示例是在背板(3U/6U)或其他机架安装单元中。

迹线阻抗

如果您没有通过电源层上的铜浇注来布线受控阻抗线,则无需太担心这一点。SPI和I2C等单端数字协议以及GPIO可通过覆铜进行布线,而无需担心阻抗,因为它们没有阻抗规格,但您仍应遵循此列表中的其他准则(如适用)。强调阻抗重要性的高速协议属于另一回事,您需要确保在这些迹线周围提供足够的铜浇注间隙,以确保不违反阻抗目标。如果电源浇注距离迹线太近,那么您需要在层堆叠中使用共面计算,以确保不会违反阻抗容差。

应用高间隙来切割平面是很危险的,因为最终会将铜切割成太多部分。如果布线太多迹线,您将在布局周围留下大量剩余的铜,这些铜被切成小部分。对于还需要阻抗控制的低层数电路板,您可能没有其他电源层可用于将所有这些部分重新连接在一起。如果您发现必须通过电源层布线大量迹线,则最好再添加两层(电源层和接地层)。

分离电源平面上的返回路径和布线

与任何其他情况下的布线一样,尤其是在电源层中布线时,请确保PCB中的信号存在明确定义的返回路径。这里的问题是,是否在相邻层中布线?在与电源区域相同的层中布线时,您将在参考平面中放置间隙。对于电源区域,这通常没问题,除非您将电源区域用作其他层中信号的参考。然后,如果您碰巧在这些间隙之一上进行布线,则会创建一个具有较高寄生电感的区域,该区域会从串扰或外部源接收更多EMI。

对于在两个平面层之间传播的速度较低的协议,只要另一层中的平面是统一的,您就可以通过分离电源平面进行布线。您创建的阻抗不连续性将是电短的,因此您无需担心反射,并且另一层上平面的存在有助于确保仍有明确的返回路径,尽管在分离平面的区域存在更高的电感。对于高速信号,这一点更为重要,您最好添加一个新层来为这些信号腾出空间,而不是切断电源层。

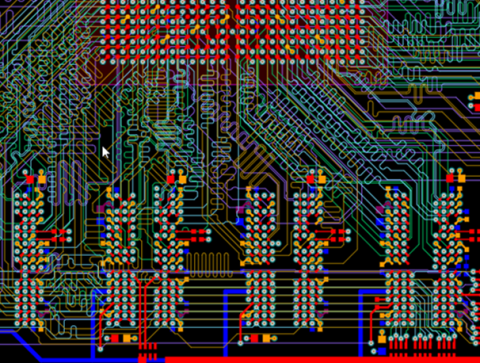

正如其他作者所指出的那样,对于更高速的协议,在平面层中的这种分离上布线带状线存在问题。例如,假设我们在电源层和接地层之间布线一条带状线。而由于电源层中的布线,接地层出现了分离。这看起来就像下面的模型。

我创建了一个非常基本的模型,可用于信号完整性仿真;信号从顶层充满接地层(L1)的焊盘开始,电源平面层(L2)中存在两个可用于布线信号的分离层。在下一个相邻信号层(L3)上,我们有两组具有定义阻抗的带状线(50欧姆单端,100欧姆差分对)。这些信号通过L4上的接地层进行布线。所有电介质厚度均为10密耳,Dk = 4/Df = 0.02。信号过孔添加了缝合过孔,以提供与每种配置中的带状线相匹配的输入阻抗。

从这个仿真模型中,我们可以看到迹线穿过分离电源层:其中一个分离层(左侧)较窄,为200密耳;另一个分离层(右侧)较宽,为400密耳。鉴于L4上存在接地平面,这将如何影响阻抗和反射?

首先,每个间隙区域都存在阻抗不连续。单端通道在间隙区域的特性阻抗为58.1欧姆,而差分通道的特性阻抗为106.2欧姆。欧姆差分特性阻抗。这种差异应该不足为奇,因为差分通道的阻抗是由该对中两条迹线之间的间距定义的。

虽然存在明显的不匹配情况,但下一个问题是,这在每个通道中是否重要。我们可以通过观察间隙区域的S参数和阻抗来确定这一点。我们预计,在低频下,间隙似乎不可见,并且不会对阻抗产生重大影响。然而,在较高频率下,我们预计间隙会导致回波损耗发生一些明显的变化。下图显示了Simbeor仿真结果,说明了超过200密耳间隙的通道布线的回波损耗(S11)。

当布线超过200密耳间隙时,结果并不那么糟糕。尽管我们通常会看到低至-30 dB或更低的回波损耗,但当达到更高的频率时,我们通常愿意接受低于-10 dB的任何回波损耗。单端和差分通道均符合这些标准,最高可达20-25 GHz。

现在,我们可以与超过400密耳间隙的布线情况进行比较,如下所示。

之前的结果已经不够理想,而这些结果和预期的一样更糟。对于在400密耳间隙上布线的差分通道和单端通道,我们仍然看到回波损耗频谱接近可接受的极限。在这些通道中,假设从-35-40 dB的基线S11开始,我们可以估算间隙会增加约20-25 dB的回波损耗,具体数值取决于频率。

如果在电源层的这些间隙中布线迹线会发生什么?应该清楚的是,上方层中的迹线会出现一些串扰。同时,电源层和接地层的存在共同决定了阻抗。串扰和反射会同时发生,并且每种情况的量在较高带宽下会更加明显。这支持了上述关于上升时间的观点——携带较慢信号的带状线可能适合在电源层的间隙上布线,但较快信号的带宽将与回波损耗频谱中的下降部分重叠,并且通道可能无法正常工作。

概括

总之,如果您使用不需要阻抗控制的低速数字信号,则无需过于担心电源覆铜中的布线迹线。只需注意电源层周围的电流路径,尽量不要将电源层切割成小岛。在其他情况下,您应该使用额外的层,并在额外的层中进行布线。此外,必要时请注意阻抗要求:如果电源层中的共面铜放置得太靠近带状线或微带线,则会产生阻抗偏差,就像我使用共面微带线展示的示例一样。

与电源层相邻的任何信号怎么样?对于中等速度的信号,必须确保附近有其他参考平面,并避免穿过电源层的间隙进行布线。对于非常快的信号,我们很快就会发现,即使有相邻的接地层(带状线配置),仍然会出现阻抗不连续性。如果电源层中的间隙较大,则在较低频率下会出现阻抗失配情况,并会产生更多反射。

Altium Designer®中的层堆栈管理器可帮助您指定PCB中的信号层和平面层,以及定义用于布线的阻抗配置文件。当设计完成并准备将文件递交给制造商时,Altium 365™平台可以轻松地协作并共享您的项目。

我们仅仅触及了在Altium 365上使用Altium Designer可能实现的功能的皮毛。立即开始免费试用Altium Designer + Altium 365。

沪公网安备 31010502006411号

沪公网安备 31010502006411号