为通道完整性应规定什么:高速链路的实用检查清单

大多数团队都是在上板调试阶段才发现通道完整性问题:仿真中看起来很干净的眼图,到了实验台上却闭合了;额定支持该数据速率的连接器,在实际拓扑中却失效了;或者一次叠层变更传导成了没人预留过的裕量损失。这些本质上都是规范失效,最终表现为信号完整性(SI)失效。解决办法是尽早将通道完整性定义为一组可测量的需求,使其足以影响架构决策,并在设计的每个阶段对这些需求进行验证。

关键要点

- 通道完整性首先是一个需求定义问题。 裕量的成败取决于拓扑、叠层和互连选择。

- 重定时器、重驱动器、连接器和线缆都会消耗你的部分通道预算。 应使用插入损耗(IL)、回波损耗(RL)、串扰和抖动等指标对它们进行规格定义,并让这些指标直接对应链路裕量。

- 测量计划是通道规范的一部分。 夹具策略和去嵌应在版图冻结之前就定义清楚。

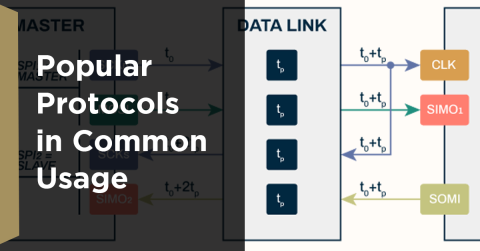

通道完整性真正涵盖什么

高速通道涵盖从发射端引脚到接收端引脚的整个电气路径,包括封装扇出、过孔、参考平面切换、走线、连接器、线缆,以及沿途的任何有源调理器件。通道完整性是指这一路径在电压、温度、工艺变化以及真实互连条件下,满足目标误码率(BER)的能力。你的拓扑、器件和验证方法都必须经得起考验,而且结果还必须可复现。

路径中的每一个元素都会消耗一部分裕量预算。只要其中任何一个规格定义不足,问题就会在后期暴露,调试周期也会变得昂贵。本文提出了一个八步流程,帮助你理解该定义哪些规格、如何定义这些规格,以及应向器件供应商提出哪些要求,从而让仿真结果与实验室测试结果趋于一致。此外,我们还为流程中的每一步提供了实用检查清单。

若想进一步了解 PCIe 7.0、800G 以太网、USB4 和 Wi-Fi 7 如何从上游推动这些需求,请参阅 高速标准不断提高门槛。

步骤 1:定义你实际要构建的链路

先从一个简短的链路定义模块开始,并将其纳入你的需求文档和测试计划中。

链路定义检查清单

- 标准和目标速率(例如:PCIe、以太网、USB4 或专有 SerDes)。

- 通道数以及通道绑定预期。

- 传输距离和拓扑。仅板内、板对板、线缆连接,还是 flyover。

- 时延预算(尤其是在你可能加入重定时器时)。

- 可能放置调理器件位置处的功耗和热约束。

- 环境和机械约束(振动、维护可达性)。

这些决策构成了后续所有选择的需求基线。尽早将它们固定下来,并保留在测试计划中。

步骤 2:在开始布局之前建立预算

通道预算是规格体系的骨架。它能把一厢情愿的设想转化为你的叠层、连接器选择和调理方案真正能够满足的硬指标。

应纳入预算的项目

- 插入损耗(IL) 相对于频率的变化。

- 回波损耗(RL) 相对于频率的变化。

- 串扰目标: 近端串扰(NEXT)、远端串扰(FEXT)以及混模指标(如果你使用这些指标)。

- 偏斜预算: 包括玻纤编织效应和连接器带来的贡献。

- 模态转换目标,因为共模能量往往会表现为 EMI。

- 抖动预算假设,以及你预计均衡能够恢复多少裕量。

如果你无法把一项需求表述为一条预算项和一个参考平面,那么你就无法对它进行清晰验证。

步骤 3:重定时器——当你需要 CDR 时该定义什么规格

当你需要时钟与数据恢复(CDR)时,重定时器会在通道中提供一个重置点。它会重新发送信号的干净版本,恢复仅靠均衡无法挽回的裕量。这种能力也带来了你需要预先定义的设计约束。

重定时器规格检查清单

- 支持的数据速率和协议。

- 通道数以及通道映射灵活性。

- 时延(典型值和最坏情况)。

- 抖动容限和抖动传递特性(器件如何滤除或传递抖动)。

- 均衡行为和控制方式:固定预设还是自适应行为;如何配置和监控。

- 功耗状态和热特性。

- 参考时钟要求(如有)。

- 信号路径要求:交流耦合预期、封装扇出约束以及布线指导。

- 模型可用性:在适用情况下提供 IBIS-AMI,以及参考设计和评估资料。

精选重定时器

Broadcom BCM85667 是一款基于 5 nm 工艺、16 通道的 PCIe Gen 6 和 CXL 3.1 重定时器,工作速率为 64 GT/s PAM4。其 产品简介 记录了支持的数据速率、分叉选项、EQ 控制和封装兼容性。这就是你在评估任何重定时器时都应期待的规格细节水平。

步骤 4:重驱动器——当你希望使用线性 EQ 时该定义什么规格

重驱动器提供线性均衡和输出调理功能,但不执行时钟恢复。这种权衡通常意味着更低的时延和更简单的集成,但对严重退化通道的修复能力较弱。

重驱动器规格检查清单

- 支持的数据速率和带宽。

- 均衡范围和步进大小。

- 输出摆幅范围和平坦增益控制。

- 噪声和线性度特性,尤其是在你可能会连同信号一起放大噪声时。

- 输入灵敏度和共模处理能力。

- 配置接口和遥测能力。

- 封装和扇出约束。

- 模型可用性和参考布局指导。

精选重驱动器

Diodes 的 PI3EQX32908ZRIEX 是一款 8 通道 PCIe 5.0 线性重驱动器,支持 5 到 32 Gbps,具备可编程的每通道 EQ、输出摆幅和平坦增益控制;同时也支持 SAS4 和 CXL 协议。

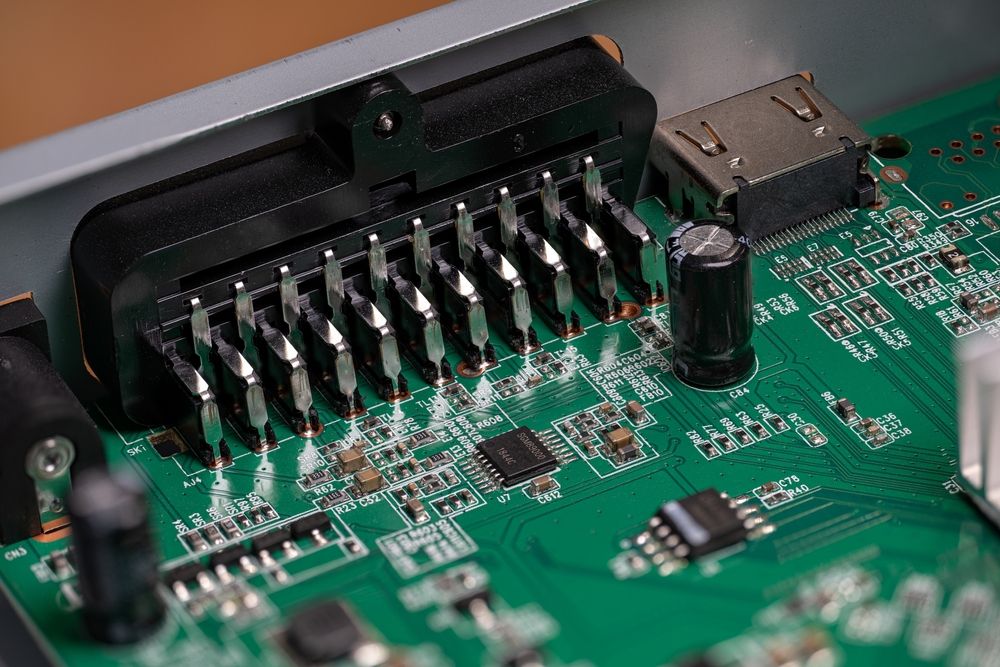

步骤 5:将连接器视为通道器件

在高速设计中,连接器及其过渡结构可能会消耗不成比例的裕量,因此它们应像其他任何通道器件一样,接受同等严格的规格定义。

连接器规格检查清单

- 差分阻抗目标及容差。

- 配对连接器以及 PCB 过渡结构的 IL 和 RL 相对于频率的变化。

- 串扰特性和针脚区域隔离指导。

- 堆叠高度选项和公差叠加。

- 插拔次数和机械耐久性假设。

- PCB 焊盘和扇出约束。

- S 参数可用性以及任何参考设计指导。

- 接口层面的第二来源方案。

精选连接器

Molex Mirror Mezz 202828-1506 是一种雌雄同体的板对板夹层连接器,具有 404 个电路、2.50 mm 堆叠高度和 BGA 焊接安装方式,支持每对差分线最高 56 Gbps 的数据速率。它采用 OCP 推荐的焊盘设计,并在整个 Mirror Mezz 系列 中共享,这意味着你可以获得 S 参数数据、焊盘文档以及分销商可见性,并将这些内容附加到你的通道模型和 BOM 审查 中。

步骤 6:线缆与 Flyover——定义通道扩展

铜缆组件和有源光学 flyover 都能将通道传输距离扩展到超出板上走线能力的范围,但它们解决的问题并不相同。铜缆作为传输线工作,受到阻抗、屏蔽和弯曲半径约束。光学 flyover 则完全绕开介质损耗,但会引入电光转换、功耗、散热和时延方面的考量。应根据你的链路预算来定义所需方案,并明确你所考虑的任何替代方案中“等效性能”意味着什么。

线缆规格检查清单

- 差分阻抗和偏斜。

- IL 和 RL 相对于频率的变化,包括两端过渡结构。

- 屏蔽效能和接地方式。

- 弯曲半径和应力释放约束。

- 插拔次数要求和维护可达性。

- 无源或有源特性(如适用)。对于光学 flyover,应定义波长、光功率预算、时延以及每通道功耗。

- 认证要求和批准线缆清单。

精选有源光学 Flyover 组件

Samtec ECUO-B04-14-015-0-2-1-2-01 (FireFly ECUO)是一种有源光学 flyover 组件,可提供每通道 28 Gbps 的 4 通道全双工收发器,或每通道 16 Gbps 的 12 通道发送器或接收器。配合 OM3 多模光纤时,传输距离可达 100 米。它完全绕过 PCB 走线损耗,并使用与 Samtec 铜质 flyover 组件 相同的微型连接器系统,因此在光学与铜缆方案之间切换时,焊盘保持不变。

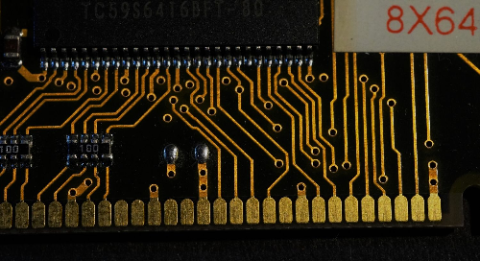

步骤 7:低损耗材料与铜箔——将叠层写入规格

更高带宽的链路要求将叠层作为受控设计输入。你的通道规范应包含材料目标值和可接受范围,并明确说明你对铜箔粗糙度和工艺能力的假设。

材料与叠层规格检查清单

- 相关频率下的 Dk 和 Df 目标值,以及允许的变化范围。

- 当导体损耗成为限制因素时,对铜箔轮廓的假设。

- 针对长距离差分走线的玻纤编织效应和偏斜风险控制。

- 如果你的环境或装配工艺要求较高,则还应定义 Tg、Td 和 Z 轴 CTE。

- 对制造商工艺能力的假设:钻孔纵横比、对位精度、过孔填充和层压次数。

- 锁定层压材料体系,并要求在任何替代之前进行明确评审。

精选低损耗层压材料

Panasonic 的 MEGTRON 7 和 Isola 的 I-Tera MT40 是高速数字通道中具有代表性的超低损耗和极低损耗层压板系列。可将这些产品作为参考基准,明确你对所选层压板的要求:稳定的电气数据、工艺指导,以及可在制造说明中明确锁定的清晰产品标识。

步骤 8. 测量计划:以相关性为目标

你的测量计划需要明确定义参考平面、夹具、校准和去嵌入方法,以便能够无歧义地将仿真结果与台架测试数据进行比较。IEEE 370-2020 是这项工作的一个实用依据,涵盖了 PCB 和互连在最高 50 GHz 表征中的数据质量、夹具注意事项以及去嵌入方法。

测量计划检查清单

- 你将测量什么: 使用 TDR 测量阻抗分布,使用 VNA 测量互连段的 S 参数,并在定义好的位置测量眼图或抖动。

- 你将在何处测量: 定义参考平面并为其命名。

- 你将如何校准: 说明校准方法及其可追溯性。

- 你将如何去嵌入: 选择与你的夹具和工具相匹配、可实际执行的方法。

- 你将如何进行相关性验证: 定义仿真与实测结果一致性的验收标准。

重点测量平台

Keysight PNA-X 网络分析仪 覆盖从 900 Hz 到 67 GHz 的频率范围(取决于具体型号),具备多个内部信号源、S 参数和噪声接收机,并兼容 Keysight 的 PLTS 软件,可用于互连表征和去嵌入。

Octopart 在工作流程中的作用

通道完整性相关器件通常真正可替代的选项更少。连接器系列、专用调理 IC 以及某些线缆组件,往往会成为拖慢构建进度的关键器件。使用 Octopart 和 BOM Tool,在设计仍具灵活性时保持以下三项信息的关联:

- 料号以及最新的生命周期状态。

- 配套资料:数据手册、模型和参考设计。

- 在封装焊盘和接口最终固化之前,提前确认替代产品和供应商选项。

越早将真实器件数据纳入通道模型,延续到布局阶段的假设就越少。连接器的 S 参数文件、retimer 产品简介,或层压板的 Dk/Df 数据表,都比一个占位符加上“稍后再定”的计划更有价值。Octopart 为你提供了一个便捷的位置,可在设计仍足够灵活、能够吸收这些发现时,检查供货情况、获取数据手册并确认生命周期状态。

避免重复改版的纪律性

通道完整性是通过你在架构设计、叠层设计和互连选择阶段做出的一系列决策建立起来的,并在布局前后通过仿真、测量和相关性验证加以确认。贯穿始终的核心原则是相同的:明确你的需求,用数字进行规格定义,选择那些有数据支撑这些指标的器件,并在布局冻结之前写好测量计划。能够持续做到这一点的团队,才是那些能够避免重复改版的团队。

沪公网安备 31010502006411号

沪公网安备 31010502006411号